核心技术特性

神经形态芯片以人脑神经网络为设计原型,通过模拟神经元与突触的工作机制实现信息处理,其最核心的优势是高度并行的分布式计算。与人脑拥有约 860 亿个神经元和 10¹⁴ 个突触连接类似,神经形态芯片集成大量模拟神经元单元(少则数千,多则百万级),各单元通过突触权重动态连接,可同时处理多维度输入信息。在图像识别任务中,传统芯片需按顺序执行算法步骤,而神经形态芯片能像人脑视觉皮层一样并行分析图像的边缘、颜色、纹理等特征,处理效率提升 10-100 倍。

超低功耗是神经形态芯片的显著标签。人脑的功耗仅约 20 瓦却能实现复杂的认知功能,神经形态芯片借鉴这一特性,采用事件驱动型计算模式 —— 仅当有新输入信息时,相关神经元才被激活,空闲单元几乎不消耗能量。一款包含 100 万个神经元的神经形态芯片,在执行语音识别任务时功耗仅 50 毫瓦,是同等算力 GPU 的 1/1000,特别适合可穿戴设备、物联网终端等低功耗场景。

自适应学习能力突破传统编程限制。神经形态芯片通过突触权重的动态调整实现自主学习,无需预先编写固定算法。例如,在机器人避障任务中,芯片可通过多次尝试自动优化神经元间的连接强度,逐渐形成最优避障策略,这种 “从经验中学习” 的能力与人脑的学习过程高度相似,摆脱了传统芯片对精确编程的依赖。

关键技术突破

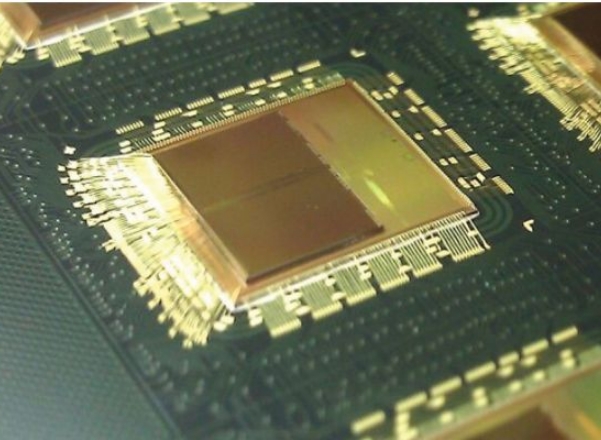

近年来,神经元单元的密度与模拟精度实现双重提升。早期神经形态芯片的神经元多为简化数字模型,功能单一,而新型混合信号神经元单元通过模拟电路复现生物神经元的脉冲发放特性,支持膜电位累积、 refractory 期等生物特性模拟,精度达到生物神经元的 90% 以上。英特尔研发的 “Loihi 2” 芯片集成了 100 万个这样的神经元单元,突触数量达 1.2 亿个,较上一代产品性能提升 10 倍,可运行更复杂的脑启发算法。

突触可塑性机制研究取得重大进展。突触权重的动态调整是学习能力的核心,新型 “忆阻器突触” 通过电阻值的连续变化模拟突触强度的长时程增强(LTP)和长时程抑制(LTD),调节精度达 8 位(256 级),且响应速度仅 10 纳秒,较传统 SRAM 突触能耗降低 99%。清华大学研发的忆阻器神经形态芯片,在 MNIST 手写数字识别任务中准确率达 98.5%,学习过程的能耗仅为 GPU 的 1/5000。

大规模神经网络协同计算成为现实。单芯片的神经元数量有限,而 “芯片级联技术” 通过高速互连链路将多颗神经形态芯片组成神经网络集群,实现百万至亿级神经元的协同计算。美国国防高级研究计划局(DARPA)的 “SyNAPSE” 项目将 1024 颗神经形态芯片级联,构建出包含 10 亿个神经元的模拟大脑,可实时处理视频流并识别动态目标,延迟低于 10 毫秒。

行业应用场景

智能边缘设备领域,神经形态芯片实现本地高效推理。华为研发的神经形态传感器芯片集成在智能摄像头中,可在设备端实时完成人脸识别、行为分析等任务,无需将数据上传云端,响应时间从云端处理的 500 毫秒缩短至 10 毫秒,同时数据隐私安全性提升 100%。在智能家居中,搭载该芯片的语音助手可在待机功耗 1 毫瓦的状态下,持续监听唤醒词,误唤醒率低于 0.1 次 / 天。

机器人领域,赋予机器环境适应能力。波士顿动力的新一代机器人搭载神经形态控制芯片,通过实时感知关节角度、受力情况等环境信息,自主调整运动姿态,在复杂地形的行走稳定性较传统控制算法提升 40%。在工业机器人中,该芯片可让机械臂通过 “试错学习” 掌握精密装配技巧,适应不同规格零件的装配需求,调试周期从 weeks 缩短至 days。

脑机接口领域,搭建人机沟通桥梁。 Neuralink 公司的脑机接口设备采用神经形态芯片作为信号处理核心,可实时解析脑电信号中的运动意图,将解析延迟从 500 毫秒降至 50 毫秒,使瘫痪患者能通过意念控制外部设备完成打字、操作机械臂等动作,字符输入速度达 90 个 / 分钟,接近正常人打字速度。

现存挑战

算法与应用生态建设滞后。神经形态芯片的计算范式与传统冯・诺依曼架构截然不同,现有人工智能算法难以直接移植,需开发专用的脑启发算法。目前成熟的神经形态算法不足 50 种,主要集中在简单识别任务,缺乏复杂逻辑推理、决策规划类算法,导致芯片的应用场景受限。建立开源算法平台和开发工具链,是推动生态发展的关键。

硬件精度与稳定性不足。模拟神经元和忆阻器突触易受温度、噪声影响,输出精度波动可达 10%,在需要高精度计算的场景中表现不佳。虽然通过冗余设计和误差校正技术可提升稳定性,但会使芯片面积增加 30%,功耗上升 50%,难以平衡性能与效率。开发新型抗噪声材料和电路结构,是提升硬件可靠性的核心方向。

大规模量产成本高昂。神经形态芯片的混合信号设计和忆阻器制造工艺复杂,良率仅为传统数字芯片的 50%,单颗百万神经元芯片的制造成本高达 1000 美元,是同规模 FPGA 的 10 倍。通过优化工艺、提升量产规模,预计 2030 年成本可降低至 200 美元以内,推动在消费电子领域的普及。

神经形态芯片正处于从技术探索向实用化过渡的关键阶段,预计 2035 年全球市场规模将突破 120 亿美元,在边缘计算、机器人、脑机接口等领域形成独特优势。随着算法生态的完善和硬件性能的提升,神经形态芯片有望实现从 “弱人工智能” 到 “强人工智能” 的跨越,最终可能构建出具备类脑认知能力的智能系统。未来,神经形态芯片与生物芯片的结合,甚至可能催生 “人工大脑”,彻底改变人类对计算和智能的认知。

- 上一篇:开启高效能计算新纪元的核心动力

- 下一篇:以光为媒的高速信息处理